# NJ1030A

Rev. 1.3 - April 2005

## **GPS Baseband Processor**

#### Datasheet

## **1** General Description

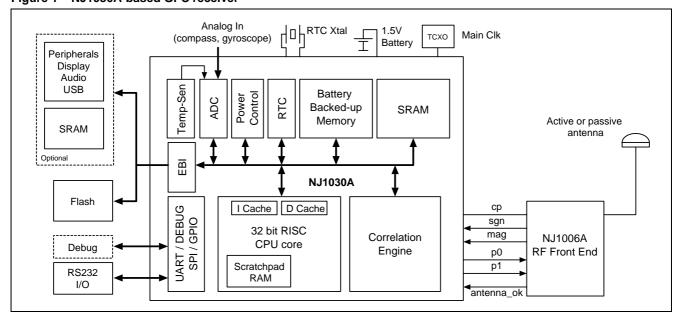

The NemeriX NJ1030A is a GPS baseband processor targeting C/A code L1 GPS low power applications and offering WAAS/EGNOS support. It is based on the NemeriX NP1016 GPS correlation core combined with a 32-bit IEEE1754 (Sparc V8) compatible CPU core, auxiliary on-chip memory, peripherals and analog blocks. Flexible configuration of system performance and memory architecture allow the NJ1030A to be used as an ultra low power GPS receiver delivering formatted navigation information (NMEA protocol with NemeriX extensions) or as a flexible GPS enabled microcontroller.

(Pb)

The GPS correlation is carried out by the NemeriX NP1016 correlator core optimized for high efficiency, low power correlation. While supporting any GPS RF front-end device with 1 bit or 2 bit output, the NJ1030A is optimized to work with the NemeriX NJ1006/A RF front ends. In particular the specific power management modes of the NJ1006/A are directly controlled. Flexible clocking schemes are implemented, making use of internal or external clock sources.

The CPU is a 32-bit RISC IEEE1754 (SPARC V8) compatible core with 32KB scratchpad RAM, 8KB instruction cache and 1KB data cache. An on chip SRAM block of 32KB is availble. A dedicated, battery backed-up, 8KB SRAM block for the storage of navigation information and a real time clock can be used to accelerate Time To First Fix (TTFF).

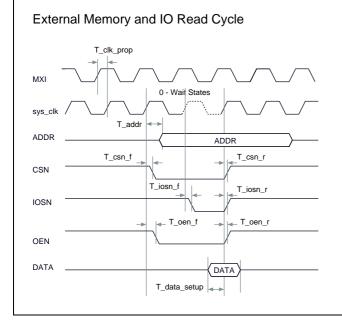

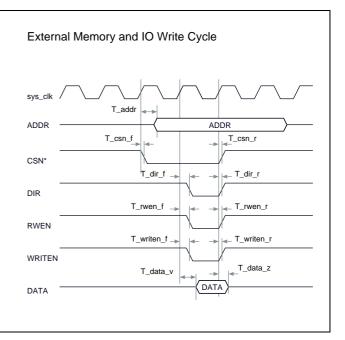

External memory and I/O space is accessed via a 32-bit external bus interface (EBI), which supports up to 4 banks of SRAM or Flash memory of 16MB each. One UART plus

optionally a master or slave SPI interface, a second UART or a general-purpose interface (GPIO) are available.

An 8 bit ,8 channels analog to digital converter is available. One of the inputs is connected to an on-chip temperature sensor that can be used to compensate the frequency drift of the local oscillator. The other seven external analog inputs can be used to integrate other sensors (such as a compass) for enhanced navigation applications.

#### 1.1 Features

- Single-chip, standalone GPS baseband processor

- Ultra low power: < 25 mW in fully active operation

- 16 low power correlation modules

- WAAS/EGNOS support

- 32-bit, royalty free, processor (Sparc V8 compatible)

- 32 KB of SRAM

- 32KB of scratch pad RAM

- 8 KB battery backed up SRAM and real time clock

- UART and a selectable UART/SPI/GPIO interface

- 32/16 or 8 bit external bus interface (EBI)

- 2-bit sign and magnitude GPS IF signal input

- 8 bit ADC: temperature sensor and 7 analog inputs

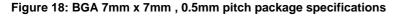

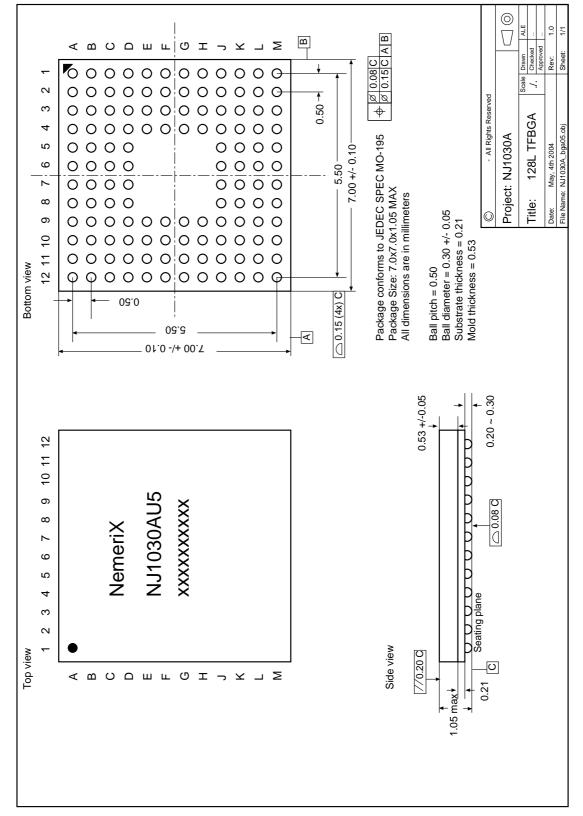

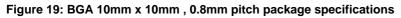

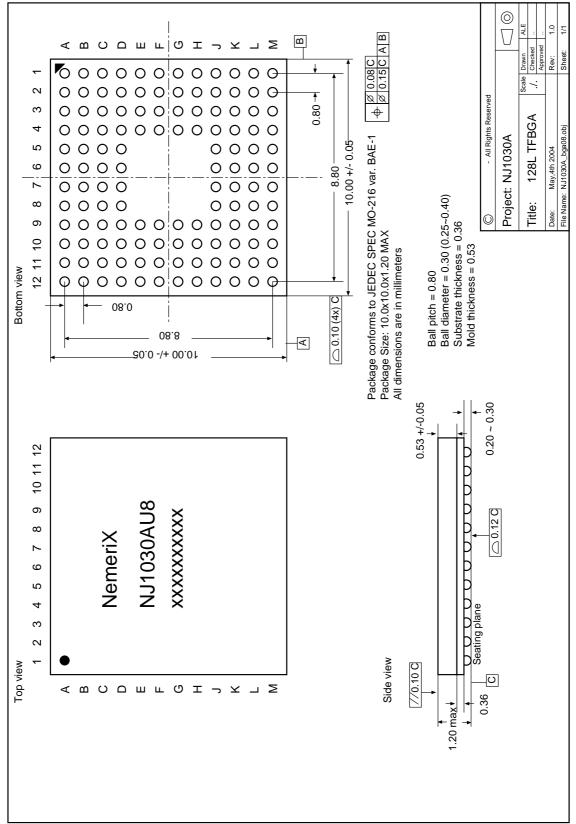

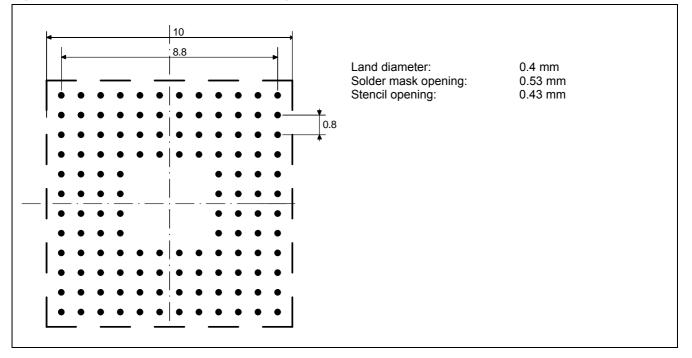

- BGA128 7x7mm and BGA128 10x10mm package

- Lead free, RoHS compliant packaging

## 1.2 Applications

- Standalone, battery-powered GPS receivers

- Tracking devices

- PDAs, Portable Media Players (PMP), digital cameras

- Cordless (Bluetooth<sup>™</sup>), remote GPS receivers

- Automotive navigation systems

© 2005 NemeriX SA. All right reserved. All trademarks and registered trademarks are property of their respective owners. The information in this datasheet is of subject to change in any manner at any time without notice. NemeriX SA assumes no responsibility for this product's use, nor for any infringement of patents or other rights from third parties which may result from its use. No license is implied under any patent or patent right by NemeriX SA. NemeriX SA, CH-6928 Manno, Switzerland. http://www.nemerix.com

NJ1030A-ds - Rev. 1.3

## Figure 1 – NJ1030A-based GPS receiver

## 2 Table of content

| 1  | General Description        | 1    |

|----|----------------------------|------|

| 2  | Table of content           | 2    |

| 3  | Absolute Maximum Ratings   | 3    |

| 4  | GPS Performance            | 4    |

| 5  | Architectural Overview     | 5    |

| 6  | Pinout Table               | 7    |

| 7  | CPU                        | . 10 |

| 8  | Clocking                   | . 12 |

| 9  | System Control Block       | . 14 |

| 10 | Interrupt Controller       | . 16 |

| 11 | Timers and Watchdog        | . 18 |

| 12 | Real Time Clock (RTC)      | . 20 |

| 13 | GPS Correlation Processor  | . 22 |

| 14 | External Memory Support    | . 25 |

| 15 | UARTs                      | . 29 |

| 16 | GPIO                       | . 31 |

| 17 | SPI Master Interface       | . 33 |

| 18 | SPI Slave                  | . 35 |

| 19 | DSU Port                   | . 37 |

| 20 | ADC                        | . 40 |

| 21 | Power Supplies             | . 41 |

| 22 | Reset Sequence             | . 41 |

| 23 | Operating Modes            | . 42 |

| 24 | Analog Signal Connection   | . 43 |

| 25 | Timings                    | . 46 |

| 26 | PCB Layout Recommendations | . 47 |

| 27 | Mounting Recommendations   | . 48 |

| 28 | Physical Dimensions        | . 49 |

|    |                            |      |

#### Absolute Maximum Ratings 3

| Max. Supply Voltage (LVDD,VBAT)             | 2.2V    |

|---------------------------------------------|---------|

| Max. Supply Voltage (all other)             | 4.0V    |

| Max. voltage on any pin0.3V to corresp. xVI | DD+0.3V |

| Max. current into any pin (except xVDD)     | ±20mA   |

| Max. current into any pin xVDD              | ±50mA   |

| EDS RatingHBM 1.5kV, CB                     | SM 250V |

| Continuous Power Dissipation       | 400mW        |

|------------------------------------|--------------|

| Operating temperature              | 40 to +85°C  |

| Junction temperature               | 125°C        |

| Storage temperature                | 65 to +150°C |

| Lead temperature (Soldering, <40s) | 260°C        |

5

ns

Absolute maximum ratings are short term stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the recommended operating conditions is not implied. Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability

ESD sensitive device: use proper precautions when handling this device.

#### **DC Electrical Characteristics**

1.6V ≤ DVDD ≤ 3.6V, 1.6V ≤ DAVDD ≤ 3.6V, 1.6V ≤ DVSU ≤ 3.6V, 1.6V ≤ TVDD ≤ 3.6V, 1.2V ≤ LVDD ≤ 1.8V, VBAT ≤ 2V, T<sub>amb</sub> = -40° to +85°C, load = 10 pF, crystal oscillator active, f<sub>sys\_clk</sub>=16.367 MHz. All voltages referred to xGND. Typical values are at xVDD = 2.5V and  $T_{amb}$ =+25°C

| Parameter                      | Conditions/description    | Min      | Тур  | Max      | Unit | Notes |

|--------------------------------|---------------------------|----------|------|----------|------|-------|

| Power Supply                   |                           |          |      |          |      |       |

| DAVDD, TVDD, DVDD              | Padring Supply Voltage    | 1.6      |      | 3.6      | V    |       |

| LVDD                           | Core Power Supply         | 1.2      |      | 2        | V    | 1     |

| DVSU                           | Power Up Unit Supply      | 1.6      |      | 3.6      | V    |       |

| VBAT                           | Battery Power Supply      | 1.1      | 1.5  | 2.0      | V    | 2     |

| I_LVDD                         | Average current with:     | 6        | 12   | 14       | mA   | 3     |

| I_DVDD                         | On-chip LVDD = 1.25V      |          |      | 3        | mA   | 3     |

| I_TVDD                         | Other xVDD = 1.8V         |          |      | 0.5      | mA   | 3     |

| I_DAVDD                        | Chip Fully Active         |          |      | 0.5      | mA   | 3     |

| I_VBAT                         | In Sleep Mode             |          | 4    |          | μA   |       |

| Power Supervisor               |                           | <u>.</u> |      |          |      |       |

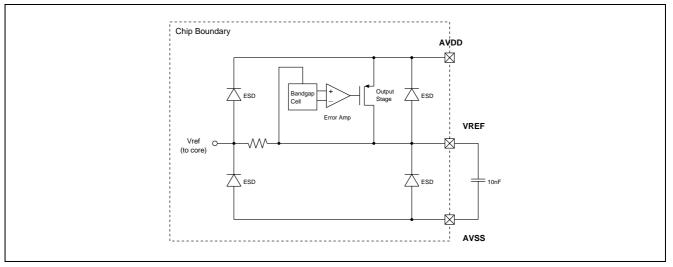

| VREF                           | Voltage reference         | 1.22     | 1.24 | 1.26     | V    |       |

| VSI                            | Voltage Superv. Threshold |          | VREF |          | V    |       |

| I_HYST                         | Hysteresis Current        | 1.1      | 1.6  | 2.1      | μA   | 4     |

| Battery OK Flag Threshold      | VBAT Rising               |          | 1.15 |          | V    |       |

|                                | VBAT Falling              |          | 1.10 |          | V    |       |

| AC Electrical Characteristics  |                           |          |      |          |      |       |

| Sys Clock Frequency            | LVDD = 1.8V               | 0        |      | 98.2     | MHz  |       |

|                                | LVDD = 1.2V external      | 0        |      | 32.4     | MHz  |       |

|                                | LVDD = 1.2V on chip       | 0        |      | 16.3     | MHz  |       |

| Sys Clock Crystal Drive Level  |                           |          | 10   |          | μW   |       |

| RTC Clock Crystal Drive Level  |                           |          | 100  |          | nW   |       |

| Clock Input Level Clipped Sine |                           | 100      |      |          | mV   | 5     |

| Digital Interfaces             |                           |          |      |          |      |       |

| VIH                            |                           | 0.7 DVDD |      |          | V    |       |

| VIL                            |                           |          |      | 0.3      | V    |       |

| VOH                            | loh = -50 μA              | 0.9 DVDD |      |          | V    |       |

| VOL                            | lol = 50 μÅ               |          |      | 0.1 DVDD | V    |       |

| Output Rise Time               | Cload = 15 pF             |          |      | 5        | ns   |       |

Output Rise Time Cload = 15 pF Cload = 15 pF Output Fall Time

Note 1: Core (LVDD) may be supplied by the internal voltage regulator.

Note 2: Guarantees NVRAM data retention and RTC operation.

**Note 3:** CPU executing GPS positioning, driving a NJ1006 RF front end with a 16.367 MHz clock **Note 4:** Hysteresis current is turned on when VSI>VREF (See section 22.2).

Note 5: X<sub>osc</sub> used also as TCXO buffer.

## 4 GPS Performance

All performance data refer to a NJ1030A used with a NJ1006/A RF front end and the antenna used in the

DK1030 GPS development kit and running version 3.x of the NS1030 GPS software.

| Item                             |                                            | Values               |              | Conditions/Notes                                                          |  |

|----------------------------------|--------------------------------------------|----------------------|--------------|---------------------------------------------------------------------------|--|

|                                  |                                            | Average              |              |                                                                           |  |

| Initial<br>Acquisition           | Cold Start                                 | 46 s                 |              | Open-sky, 24 hrs statistic, active antenna (signal range is               |  |

| Time [s]                         | Warm Start                                 | 34 s                 |              | between 30 to 49 dB/Hz).                                                  |  |

|                                  | Hot Start                                  | 5 s                  |              |                                                                           |  |

| Fix Time After<br>Obscuration[s] | Obscuration Time 1s to 100 s               | < 3 s                |              | Maximum Sensitivity -147 dBm                                              |  |

| Acquisition<br>Sensitivity (fix  | TTFF [Hot] with all signals at –138 dBm    | 30 s                 |              | Simulator Test, all signals at specified power level.                     |  |

| not available)<br>[dBm]          | TTFF [Hot] with all<br>signals at –141 dBm | 41 s                 |              |                                                                           |  |

| Acquisition Sensi                | tivity (fix available) [dBm]               | –147 dBm             |              | Estimated.                                                                |  |

| Tracking Sensitiv                | ity [dBm]                                  | Better than –150 dBm |              | Simulator Test, continuous fix with all signals at specified power level. |  |

|                                  | Static CEP 50                              | 1.2 m                | 0.8 m (WAAS) |                                                                           |  |

| Static Accuracy                  | Static CEP 95                              | 3.0 m                | 2.0 m (WAAS) | Open-sky, 24 hrs statistic,<br>active antenna (signal range is            |  |

|                                  | Static Altitude 50                         | 1.3 m                | 0.8 m (WAAS) | between 30 to 49 dB/Hz).                                                  |  |

|                                  | Static Altitude 95                         | 3.8 m                | 3.0 m (WAAS) |                                                                           |  |

| Maximum Speed                    | [m/s]                                      | 515 m/s              |              |                                                                           |  |

| Maximum Accele                   | ration [g]                                 | 2 g                  |              |                                                                           |  |

| Maximum Altitude                 | e [m]                                      | 18000                |              |                                                                           |  |

## 5 Architectural Overview

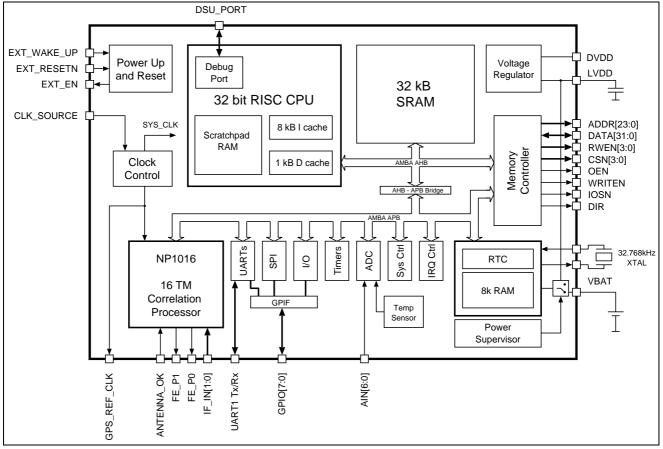

## Figure 2. NJ1030A Block diagram

This chapter briefly describes the main building blocks of the NJ1030A. A more detailed description of all blocks and their sub-blocks can be found in the following chapters.

## 5.1 CPU

The NJ1030A CPU is a royalty free, 32bit RISC processor conforming to the IEEE\_1754 (SPARC V8) architecture. It is designed for embedded applications and provides the following features:

- 5 stages pipelined architecture

- single cycle 32 bit hardware multiplier

- barrel shifter

- radix 2 hardware divider

- 8 windows register file

- 8 kBytes instruction cache, 1 kBytes data cache

- 32 KBytes scratch pad memory

- AMBA AHB and APB compatible interface

- Debug port (DSU)

The scratch pad RAM is a block of 32kB memory dedicated to data, that is directly connected to the CPU core at the same level as the D-Cache. As a consequence it has the quickest poosible access time. At firwmare build time, critical data structures can be assigned to the scratch pad RAM area.

#### 5.2 On Chip SRAM

A block of 32kBytes 0-wait states SRAM is available on chip, on the fast AHB bus. This allows critical code portions

as well as data structures to be stored. The on-chip SRAM content is cachable (both instructions and data). This memory supports 8,16 and 32 bit access mode.

#### 5.3 Battery Backed up Memory

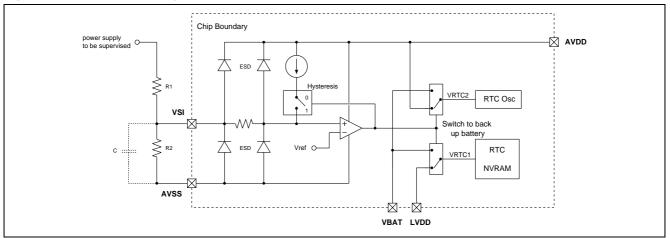

In order for the software to store recent GPS almanac data at boot time, the NJ1030A has a block of 8 kBytes of battery backed-up and write protected SRAM (NVRAM). The power supply of this memory block is monitored by the integrated power supervisor. This memory area can also be used to store relevant system status information before entering power management modes that involve the removal of the power supply. Only 32 bit access is supported.

## 5.4 External Bus Interface (EBI)

The EBI directly supports up to 4 banks of 16 MBytes of asynchronous memory, with a fifth bank optionally accessible through signals of the GPIO interface. Each bank can individually be set to implement an 8, 16 or 32 bit access mode with a selectable number of wait states.

When 16 or 32 bit memory components are used in the sytem, the NJ1030A memory interface allows access to individual bytes by means of byte enable signals, typically provided by state of the art 16 or 32 bit SRAMs.

## 5.5 Clocking

The main system clock can be generated by an on chip oscillator, by a TCXO or be an external digital clock. This is the clock used for all the NJ1030A functions, excluding the GPS correlation that has a dedicated clock derived internally from the system clock (with a division factor from 1 to 8). This allows for flexible frequency plans to be implemented, with the possibility to trade off between the computational requirements of the application, the GPS frequency plan and the power consumption requirements.

## 5.6 GPS Correlation Unit

The GPS correlation function is carried out by the correlation unit which is a 16 tracking modules (64 correlators) implementation of the NemeriX NP1016 GPS correlator IP core. The NP1016 is connected to the CPU as an AMBA APB peripheral. Two GPS interrupt signal (ACC\_INT and MEAS\_INT) are connected to the CPU interrupt controller. The correlation block is clocked by a dedicated clock (NP1016\_GPS\_CLK) signal derived from the main SYS\_CLK, which can be deactivated when the GPS functionality is not needed by the system.

The correlation unit provides:

- 16 C/A-code acquisition and tracking modules (TMx)

- WAAS/EGNOS support

- 2-bit sign and magnitude signal input

- Programmable interrupt interval and measurement rate

- Individual tracking-module activation

- Power management modes

- Direct control of the NJ1006/A RF front end power management features

- Fast acquisition mode (FAM)

## 5.7 Other Peripherals

- UARTs : two serial interfaces are available. UART1 is always available on dedicated pins, while a second UART2 shares the pins of the GPIO interface. UART1 has a 16 bytes receive and send FIFO, while UART 2 has a 4 bytes send and receive FIFO. The UART1 lines can also be configured to act as DSU UART lines, allowing for flash re-programming reusing the buffer and connectors of UART1, without the need to access the dedicated DSU pins.

- **SPI**: both master and slave SPI interface alternatively are supported, by sharing the same pins of the GPIO interface. The SPI master supports up to 2 slaves. The slave has a send and receive buffer of 16 bytes.

- **Timers**: two 24-bit timers are provided on-chip. The timers can work in periodic or one-shot mode. Both timers are clocked by a common 10-bit prescaler.

- Watchdog: a 24-bit watchdog is provided on-chip. The watchdog is clocked by the timer prescaler. When the watchdog reaches zero, an output signal (WDOG) is asserted. If enabled, this signal can be used to generate system reset.

- Interrupt controller : it manages a total of 15 interrupts, originating from internal and external sources. Each interrupt can be programmed with a two levels priority. Internal and external interrupt sources are used.

- Analog to Digital Converter (ADC): an 8 bit resolution 8 channels ADC is available with 7 analog inputs directly

connected to the pads and one input connected to an on chip temperature sensor.

• **RTC**: a pseudo real time clock block with 1 second precision, 30 bits wide register is implemented. It also offers a wake up functionality that can be used to recover the system from power down modes. The RTC has an on chip oscillator that uses a 32 kHz quartz.

## 5.8 GPIO Interface

An 8 bit general purpose I/O interface allows for parallel I/O. This interface can be reconfigured in order to share some lines with other peripherals.

## 5.9 GPS IF Interface

This dedicated interface consist of 2 bits input (sign and magnitude), two power mode control signals for the NJ1006/A RF front ends, the GPS clock and an antenna ok input signal. The GPS IF interface also has a dedicated power supply (TVDD).

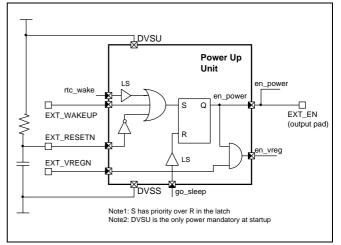

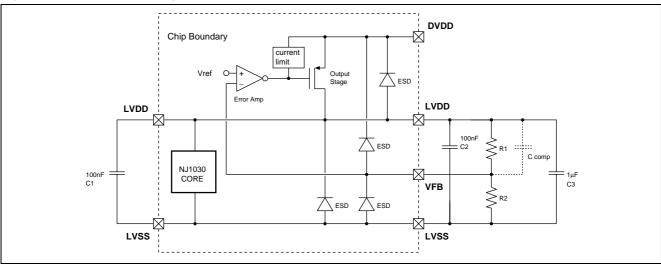

## 5.10 Power Supplies

Different power supplies for pad ring and core can be used, with the possibility to generate the core power supply by an on chip voltage regulator. The core voltage can be adjusted between 1.2V and 1.8V, depending on the clock frequency being used. The on chip voltage regulator can also be disabled if an external power supply is available in the system.

The digital pad ring power supply can be between 1.8V and 3.3V (DVDD), with the possibility also to use an independent level for the IF interface (TVDD). In power down mode a third digital power supply is used to maintain a tiny portion of the logic ready to wake up the NJ1030A and the attached components (DVSU).

For the battery backed up memory and the RTC a dedicated power supply is used. The power supervisor can be programmed to monitor the used core or padring power supply. In case of faillure of the monitored power supply, the power supervisor will switch the power supply source to battery for the RTC and battery backed up memory as soon as the programmed threshold is reached.

## 5.11 Power Down Modes

Beside fully active operation, where individual peripherals are clocked only depending on their activity, the NJ1030A supports clock-on-demand and SLEEP modes.

The SLEEP mode is entered by the CPU when a period of complete system inactivity can be expected. At this point the CPU can turn off the core power supply as well as other external components. Only a tiny portion of logic is kept powered and will reboot the system at the occurrence of a RTC wake up or an external wake up or reset.

The clock on demand option can be enabled individually for some of the clock sub-domains of the NJ1030A. When clock on demand is enabled, each block controls the gating of its own clock. One of the typical use of the clock on demand mode is for the CPU to stop it own clock, when no further processing is needed. When an interrupts from a peripheral occurs, then the CPU clock is switch on again, the interrupt is serviced and processing is resumed.

## 6 NJ1030 A Pinout

## **Pinout Table**

| Pin Nb | Ball Nb | Signal                      | Туре           | Description                                          | LVDD=0 status    |

|--------|---------|-----------------------------|----------------|------------------------------------------------------|------------------|

| 1      | C4      | DATA[4]                     | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 2      | C3      | DATA[5]                     | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 3      | C2      | DATA[6]                     | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 4      | C1      | DATA[7]                     | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 5      | D4      | DATA[8]                     | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 6      | D3      | DATA[9]                     | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 7      | D2      | DATA[10]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 8      | D1      | DATA[11]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 9      | E4      | DATA[12]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 10     | E3      | DATA[13]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 11     | E2      | DATA[14]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 12     | E1      | DATA[15]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 13     | F2      | DATA[16]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 14     | F3      | DATA[17]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 15     | F1      | LVDD                        | Digital power  | Core power supply                                    |                  |

| 16     | F4      | LVSS                        | Digital ground | Ground                                               |                  |

| 17     | G1      | DATA[18]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 18     | G2      | DATA[19]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 19     | G3      | DATA[20]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 20     | H1      | DATA[21]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 21     | G4      | DVDD                        | Digital power  | Power supply for padring and voltage reg.            |                  |

| 22     | H4      | DAVSS                       | Digital gnd    | Ground                                               |                  |

| 23     | H3      | DATA[22]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 24     | H2      | DATA[23]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 25     | J1      | DATA[24]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 26     | J2      | DATA[25]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 27     | J3      | DATA[26]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 28     | J4      | DATA[27]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 29     | K1      | DATA[28]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 30     | K2      | DATA[29]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 31     | K3      | DATA[30]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 32     | K4      | DATA[31]                    | Digital IO     | EBI Data Bus                                         | Z + keeper       |

| 33     | L1      | DIR                         | Digital Out    | EBI Data Bus direction                               | 0                |

| 34     | M1      | OEN                         | Digital Out    | EBI Output Enable                                    | 1                |

| 35     | M2      | IOSN                        | Digital Out    | EBI I/O Space chip select                            | 1                |

| 36     | L2      | WRITEN                      | Digital Out    | EBI I/O Space Write Enable                           | 1                |

| 37     | L3      | RWEN[0]/BEN[0] <sup>4</sup> | Digital Out    | EBI RAM Write Strobe / Byte enable                   | 1                |

| 38     | M3      | RWEN[1]/BEN[1] <sup>4</sup> | Digital Out    | EBI RAM Write Strobe / Byte enable                   | 1                |

| 39     | L4      | RWEN[2]/BEN[2] <sup>4</sup> | Digital Out    | EBI RAM Write Strobe / Byte enable                   | 1                |

| 40     | M4      | RWEN[3]/BEN[3] <sup>4</sup> | Digital Out    | EBI RAM Write Strobe / Byte enable                   | 1                |

| 41     | J5      | CSN4                        | Digital Out    | EBI RAM4 Chip Select                                 | 1                |

| 42     | K5      | CSN0                        | Digital Out    | EBI RAM0 Chip Select (Boot)                          | 1                |

| 43     | L5      | CSN1                        | Digital Out    | EBI RAM1 Chip Select                                 | 1                |

| 44     | M5      | CSN2                        | Digital Out    | EBI RAM2 Chip Select                                 | 1                |

| 45     | J6      | CLK_SOURCE <sup>1</sup>     | Digital In     | Clock source type selector                           |                  |

| 46     | K6      | EXT_WAKE_UP1                | Digital In     | External Wake Up Signal                              |                  |

| 47     | L6      | EXT_RESETN <sup>1</sup>     | Digital In     | Active Low Asynchronous Reset                        |                  |

| 48     | M6      | EXT_EN <sup>1</sup>         | Digital Out    | Enable for ext components                            | LVDD independent |

| 49     | L7      | EXT_VREGN <sup>1</sup>      | Digital In     | Internal (1)/External (0) voltage regulator selector |                  |

| 50     | K7      | DVSU                        | Digital power  | Independent power supply for Power-up unit           |                  |

| 51     | M7      | TVDD                        | Digital power  | RF interface power supply                            |                  |

| 52     | J7      | TVSS                        | Digital ground | RF interface ground                                  |                  |

| 53     | M8      | GPS_REF_CLK <sup>2</sup>    | Digital Out    | GPS reference clock output 1                         |                  |

| 54     | J8      | ANTENNA_OK <sup>2</sup>     | Digital In     | Antenna status indicator                             |                  |

| 55     | L8      | MAG <sup>2</sup>            | Digital In     | GPS IF input signal (magnitude)                      | 1                |

| 56       | K8       | SGN <sup>2</sup>              | Digital In     | GPS IF input signal (sign)                |            |

|----------|----------|-------------------------------|----------------|-------------------------------------------|------------|

| 57       | K9       | FE_P0 <sup>2</sup>            | Digital Out    | Power control signal to RF                | 0          |

| 58       | J9       | FE_P1 <sup>2</sup>            | Digital Out    | Power control signal to RF                | 0          |

| 59       | L9       | VSI <sup>3</sup>              | Analog In      | Power supervisor analog input             | 0          |

| 60       | M9       | DAVDD                         | Analog power   | Analog power supply                       |            |

| 61       | L10      | AVSS                          | Analog gnd     | Analog ground                             |            |

| 62       | M10      | VREF <sup>3</sup>             | Analog Out     | Voltage reference                         |            |

| 63       | M10      | MXI <sup>3</sup>              | Analog/Dig. In | Digital Clock input or Crystal            |            |

| 64       | M12      | MXO <sup>3</sup>              | Analog Out     | TCXO input or Crystal                     |            |

| 65       | J10      | AIN[3] <sup>3</sup>           |                | Analog signal input to ADC                |            |

| 66       | K10      | AIN[3]                        | Analog In      |                                           |            |

| 67       |          | AIN[1]<br>AIN[5] <sup>3</sup> | Analog In      | Analog signal input to ADC                |            |

|          | L11      | AIN[5]<br>AIN[0] <sup>3</sup> | Analog In      | Analog signal input to ADC                |            |

| 68<br>69 | K11      |                               | Analog In      | Analog signal input to ADC                |            |

|          | J11      | AIN[4] <sup>3</sup>           | Analog In      | Analog signal input to ADC                |            |

| 70       | L12      | AIN[2] <sup>3</sup>           | Analog In      | Analog signal input to ADC                |            |

| 71       | K12      | AIN[6] <sup>3</sup>           | Analog In      | Analog signal input to ADC                |            |

| 72       | H10      | AVSS                          | Analog ground  | Analog ground                             |            |

| 73       | J12      | RXI                           | Analog In      | RTC Crystal Input                         |            |

| 74       | H12      | RXO                           | Analog Out     | RTC Crystal Out                           |            |

| 75       | H11      | VBAT                          | Analog power   | Back-up battery                           |            |

| 76       | H9       | TEST_MODE[1]                  | Digital In     | Reserved                                  |            |

| 77       | G11      | TEST_MODE[0]                  | Digital In     | Reserved                                  |            |

| 78       | G10      | DSU_MUX                       | Digital In     | UART1/DSU select                          |            |

| 79       | G9       | LVSS                          | Digital ground | Ground                                    |            |

| 80       | G12      | LVDD                          | Digital power  | Core power supply                         |            |

| 81       | F12      | VFB                           | Analog In      | Voltage regulator feedback                |            |

| 82       | F11      | DSUACT                        | Digital Out    | Debug Support Unit (Active)               | 1          |

| 83       | F10      | DSUEN                         | Digital In     | Debug Support Unit (Enable)               |            |

| 84       | F9       | DSURX                         | Digital In     | Debug Support Unit (Receive)              |            |

| 85       | E10      | DSUBRE                        | Digital In     | Debug Support Unit (Break)                |            |

| 86       | E11      | DSUTX                         | Digital Out    | Debug Support Unit (Transmit)             | 1          |

| 87       | E9       | DAVSS                         | Digital ground | Ground                                    |            |

| 88       | D9       | DVDD                          | Digital power  | Padring power supply                      |            |

| 89       | E12      | GPIO[0]                       | Digital IO     | Programmable GPIO interface               | Z + keeper |

| 90       | D12      | GPIO[1]                       | Digital IO     | Programmable GPIO interface               | Z + keeper |

| 91       | D11      | GPIO[2]                       | Digital IO     | Programmable GPIO interface               | Z + keeper |

| 92       | D10      | GPIO[3]                       | Digital IO     | Programmable GPIO interface               | Z + keeper |

| 93       | C11      | GPIO[4]                       | Digital IO     | Programmable GPIO interface               | Z + keeper |

| 94       | C10      | GPIO[5]                       | Digital IO     | Programmable GPIO interface               | Z + keeper |

| 95       | C12      | GPIO[6]                       | Digital IO     | Programmable GPIO interface               | Z + keeper |

| 96       | B11      | GPIO[7]                       | Digital IO     | Programmable GPIO interface               | Z + keeper |

| 97       | B12      | UART1_RX                      | Digital In     | UART1 Receive                             | ·          |

| 98       | A12      | UART1_TX                      | Digital Out    | UART1 Transmit                            | 1          |

| 99       | C9       | ADDR[23]                      | Digital Out    | EBI Address                               | 1          |

| 100      | A11      | ADDR[22]                      | Digital Out    | EBI Address                               | 1          |

| 101      | B10      | ADDR[21]                      | Digital Out    | EBI Address                               | 1          |

| 102      | A10      | ADDR[20]                      | Digital Out    | EBI Address                               | 1          |

| 103      | B9       | ADDR[19]                      | Digital Out    | EBI Address 1                             |            |

| 104      | A9       | ADDR[18]                      | Digital Out    | EBI Address 1                             |            |

| 105      | D8       | ADDR[17]                      | Digital Out    | EBI Address 1                             |            |

| 106      | C8       | ADDR[16]                      | Digital Out    | EBI Address 1                             |            |

| 107      | B8       | ADDR[15]                      | Digital Out    | EBI Address 1                             |            |

| 107      | A8       | ADDR[14]                      | Digital Out    | EBI Address 1                             |            |

| 100      | B7       | ADDR[13]                      | Digital Out    | EBI Address 1                             |            |

| 109      | C7       | ADDR[13]                      | Digital Out    | EBI Address 1<br>EBI Address 1            |            |

| 111      | D7       | DAVSS                         | Digital ground | Ground                                    | I          |

| 112      | D7<br>D6 | DVDD                          | Digital power  | Power supply for padring and voltage reg. |            |

|          |          |                               | ů l            |                                           | 1          |

| 113      | A7       | ADDR[11]                      | Digital Out    | EBI Address                               | 1          |

| 114 | B6 | ADDR[10] | Digital Out | EBI Address  | 1          |

|-----|----|----------|-------------|--------------|------------|

| 115 | C6 | ADDR[9]  | Digital Out | EBI Address  | 1          |

| 116 | A6 | ADDR[8]  | Digital Out | EBI Address  | 1          |

| 117 | A5 | ADDR[7]  | Digital Out | EBI Address  | 1          |

| 118 | B5 | ADDR[6]  | Digital Out | EBI Address  | 1          |

| 119 | C5 | ADDR[5]  | Digital Out | EBI Address  | 1          |

| 120 | D5 | ADDR[4]  | Digital Out | EBI Address  | 1          |

| 121 | A4 | ADDR[3]  | Digital Out | EBI Address  | 1          |

| 122 | A3 | ADDR[2]  | Digital Out | EBI Address  | 1          |

| 123 | A2 | ADDR[1]  | Digital Out | EBI Address  | 1          |

| 124 | A1 | ADDR[0]  | Digital Out | EBI Address  | 1          |

| 125 | B4 | DATA[0]  | Digital IO  | EBI Data Bus | Z + keeper |

| 126 | B3 | DATA[1]  | Digital IO  | EBI Data Bus | Z + keeper |

| 127 | B2 | DATA[2]  | Digital IO  | EBI Data Bus | Z + keeper |

| 128 | B1 | DATA[3]  | Digital IO  | EBI Data Bus | Z + keeper |

Note 1: Pads under DVSU power supply.

Note 2: Pads under TVDD power supply.

Note 3: Pads under DAVDD power supply.

Note 4: The function changes by activating the Byte Enable function on the EBI (see 12.6)

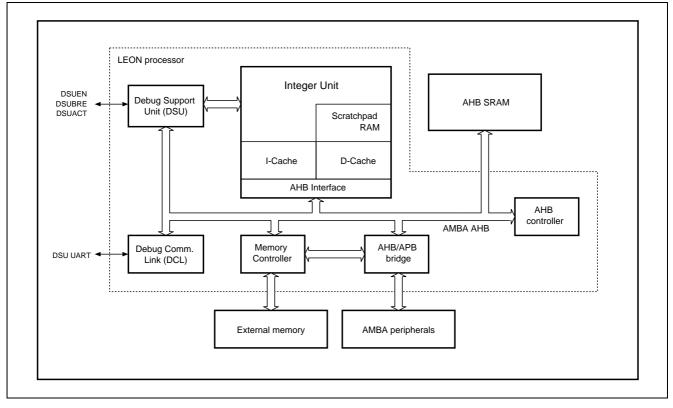

## 7 CPU

Figure 3 Leon block diagram

The following section gives a general overview of the Leon's building blocks. More details can be found in the next chapters or in the online Leon and Sparc V8 documentation available at <a href="http://www.gaisler.com">http://www.gaisler.com</a>. The Leon version implemented in the NJ1030A design is 1.0.16.

## 7.1 Integer Unit

The LEON integer unit implements the full SPARC V8 instruction set, including all multiply and divide instructions. The number of register windows used in the NJ1030A is 8 (see Sparc V8 reference).

## 7.2 Cache Sub-System

The Leon is configured with 8 kBytes of direct mapped instruction cache and 1 kByte of direct mapped data cache. The instruction cache uses streaming during line-refill to minimise refill latency. The data cache uses write-through policy and implements a double-word write-buffer.Debug Support Unit

The debug support unit (DSU) allows debugging on target hardware and has negligible impact on performance. The DSU allows inserting breakpoints and access to all on-chip registers from a remote debugger. Communication to an outside debugger (e.g. gdb) is done using a dedicated UART (RS232).

## 7.3 Watchpoint Registers

To aid software debugging, four watchpoints registers are available. Each register can cause a trap on an arbitrary instruction or data address range. If the debug support unit is enabled, the watchpoints can be used to enter debug mode.

## Memory Map

| Address Space           | Size  | Mapping            | Chip Select       | Cacheable |

|-------------------------|-------|--------------------|-------------------|-----------|

| 0x00000000 - 0x00FFFFFF | 16 M  | RAM0 (boot)        | CSN0              | I and D   |

| 0x01000000 - 0x01FFFFFF | 16 M  | RAM1               | CSN1              | I and D   |

| 0x02000000 - 0x02FFFFFF | 16 M  | RAM2               | CSN2              | I and D   |

| 0x03000000 - 0x03FFFFFF | 16 M  | RAM3               | CSN3 <sup>1</sup> | I and D   |

| 0x04000000 - 0x0FFFFFFF | 192 M | Unused             | Unused            | I and D   |

| 0x10000000 - 0x10FFFFFF | 16 M  | RAM4               | CSN4              | I and D   |

| 0x11000000 - 0x1FFFFFFF | 240 M | Unused             | Unused            | I and D   |

| 0x20000000 - 0x20FFFFFF | 16 M  | IO0                | IOSN              | no        |

| 0x21000000 - 0x2FFFFFFF | 16 M  | IO0 (echo)         | IOSN              | no        |

| 0x30000000 - 0x6FFFFFF  | 16 M  | IO0 (echo)         | IOSN              | I only    |

| 0x70000000 - 0x7FFFFFFF | 32 K  | AHBSRAM            | -                 | I and D   |

| 0x80000000 - 0x8FFFFFF  | 256 M | APB area           | -                 | -         |

| 0x90000000 - 0x9FFFFFF  | 256 M | Debug Support Unit | -                 | -         |

| 0xA0000000 - 0xAFFFFFFF | 32 K  | Scratchpad RAM     | -                 | no        |

Note 1: Available through GPIO interface (GPIO[2]).

## **APB Register Mapping**

| Slave Id | Function               | Internal Amba bus address |

|----------|------------------------|---------------------------|

| 0        | Memory controller      | 0x8000000 - 0x8000008     |

| 1        | AHB status reg         | 0x8000000C - 0x80000010   |

| 2        | Cache controller       | 0x80000014 - 0x80000014   |

| 3        | Write protection       | 0x8000001C - 0x80000020   |

| 4        | Configuration register | 0x80000024 - 0x80000024   |

| 5        | Timers                 | 0x80000040 - 0x8000005C   |

| 6        | UART 1                 | 0x80000070 - 0x8000007C   |

| 7        | UART 2                 | 0x8000080 - 0x800008C     |

| 8        | Interrupt CTRL         | 0x80000090 - 0x8000009C   |

| 9        | I/O Port               | 0x80000A0 - 0x80000AC     |

| 10       | Temperature sensor     | 0x800000B0 - 0x800000BC   |

| 11       | DSU UART               | 0x800000C0 - 0x800000CC   |

| 12       | SPI Master             | 0x800000D0 - 0x800000DC   |

| 13       | SPI Slave              | 0x800000E0 - 0x800000E8   |

| 14       | System CTRL Block      | 0x800000F0 - 0x800000FC   |

| 15       | NP1016                 | 0x80001000 - 0x80001FFC   |

| 16       | NVRAM                  | 0x80002000 - 0x80003FFC   |

|          | RTC <sup>1</sup>       | 0x80008000 - 0x8000800C   |

Note 1 : The NVRAM memory and the RTC module share the same APB slave peripheral.

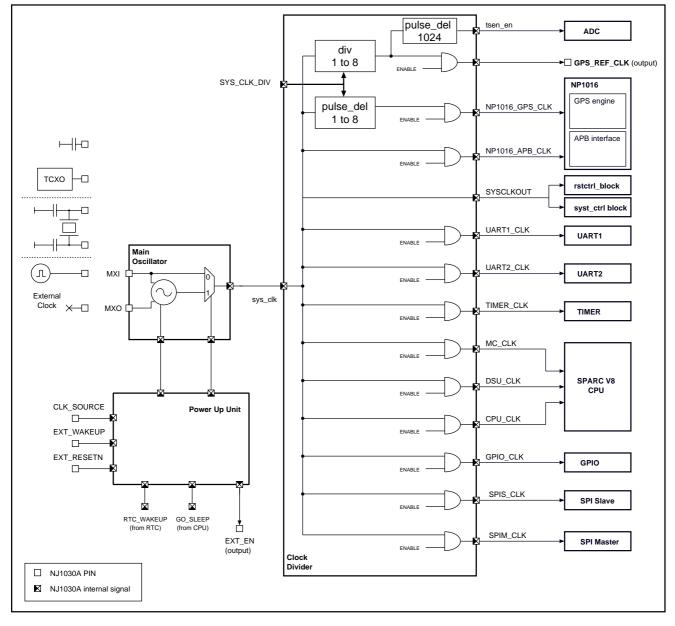

## 8 Clocking

## Figure 4 Clocking scheme

The main clock (SYS\_CLK) can be generated either by:

- the on-chip crystal oscillator (Xosc).

- a temperature compensated oscillator (TCXO).

- an external digital clock.

- the RF front-end oscillator (full swing).

All along the datasheet, the following rule has been adopted: an 'internally generated clock' refers to a Xosc or a TCXO. An 'externally generated clock' refers to any clock source that can be directly used by the NJ1030A without being buffered (external digital clock or clock generated by the RF front-end)

The clocking of the system is flexible enough to scale the system performance depending on the application, to support a wide range of GPS frequency plans and to allow the use of different clock sources. The NJ1030A has two synchronous clock domains:

- SYS\_CLK: used for the CPU and all the peripherals except the NP1016.

- GPS\_REF\_CLK/NP1016\_GPS\_CLK: the reference clock for the RF front-end and the correlation unit. It is generated from SYS\_CLK by means of a programmable clock divider under control of the NJ1030A CPU. The clock division factor range is from 1 to 8.

The CLK\_SOURCE pin selects between an external ('0') or internal ('1') clock source.

For detailed instruction on how to connect a TCXO, a crystal oscillator or a digital clock to the NJ1030A, refer to section .

#### 8.1 Shut Down of Main Clock in SLEEP Mode

For the implementation of the SLEEP power management mode, the SYS\_CLK generation can be switched off by the CPU. The system clocking is then resumed either by an external wake up, by a system reset or by the internal RTC wake up.

If the on chip oscillator is used, then it is automatically deactivated when the system enters SLEEP mode. Moreover when the system enters SLEEP mode, the internal oscillator is always selected as the source of the clock (independently from the value of CLK\_SOURCE). This feature effectively shuts down the NJ1030A main clock even if the external clock is still running.

The EXT\_EN pin can be used to control the powering down and up of external devices when the NJ1030A is entering/exiting sleep mode.

#### 8.2 Sub-Clocks

A set of subclocks is generated from the main source. All of the following subclocks are either divided version or gated version of the main clock.

- **GPS\_REF\_CLK**: GPS reference clock available on the external pin for the GPS RF front end. It is a divided version of SYS\_CLK. Clock division factor is 1 to 8 according to the value of CLK\_DIV\_FACTOR.

- NP1016\_GPS\_CLK: pulse deleted version of SYS\_CLK. Pulse deletion factor is between 1 and 8 according to the value of CLK\_DIV\_FACTOR.

- NP1016\_APB\_CLK: gated version of SYS\_CLK that goes to the APB part of the NP1016 and that can be shut down when GPS is not needed.

- UART1\_CLK, UART2\_CLK, TIMER\_CLK, SPIM\_CLK, SPIS\_CLK, GPIO\_CLK, DSU\_CLK, CPU\_CLK and MC\_CLK (memory controller) are gated clock version of SYS\_CLK that individually clocks the corresponding subblocks.

For the temperature sensor block an enable signal that is the pulse deleted version of factor 1024 of GPS\_REF\_CLK is generated. It is used by the temperature sensor interface to drive the slow analog blocks of the sensor (DAC + comparator). This signal is also used to implement the ageing mechanism in the UARTs and SPI slave FIFOsThe gating of these clocks is controlled by a glitch free mechanism. The user has the ability to enable or disable each sub-clock individually by setting the corresponding CLK\_EN bit in the CCTRL\_REG of the system control block.

#### 8.3 Clock on demand mechanism

Each APB peripheral can dynamically require the activation of its own sub-clock. This mechanism achieves major power savings since the sub-clocks are activated only when needed by the respective blocks. For each subclock, the "clock demand" feature is enabled by a dedicated bit (DMD\_EN) in the CCTRL\_REG of the system control block.

When the two bits (CLK\_EN and DMD\_EN) of a given block are at '1', then the sub-block can generate a demand signal that activates its own sub-clock.

This mechanism is used by the UART controllers to finish the transmission even if the CPU is asked to deactivate the clock. The same mechanism applies to a UART that is starting to receive data, when no clock is present. The demand signal permits to get the UART clock running, to generate an interrupt and resume the CPU activity.

The NP1016 clocking requires peripherals to be used with a '11' (for CLK\_EN and DMD\_EN) configuration for both the NP1016\_APB\_CLK and the NP1016\_GPS\_CLK, in order for the low power features to be active. If the CLK\_EN bit is cleared for these clocks, then the NP1016 has always all clocks inactive, independently from the number of active tracking modules.

Setting DMD\_EN for the CPU\_CLK enables the CPU clock to be halted, however the CPU clock will be maintained until the current memory access has been completed, therefore after setting this flag the CPU should execute NOPs to allow any pending accesses to complete. After this the CPU clock will be stopped until an interrupt occurs, this will clear the DMD\_EN bit enabling the CPU to continue execution, which will begin with the execution of the trap handler for the pending interrupt.

#### Sub-Clock Domains

| Clock Domain                                  | Demand signal generation                                                                    |

|-----------------------------------------------|---------------------------------------------------------------------------------------------|

| GPS_REF_CLK                                   | Demand signal always at '1'                                                                 |

| NP1016_APB_CLK                                | Demand signal based on the read/write activity on APB                                       |

| NP1016_GPS_CLK                                | Demand signal based on the transfer activity on the APB                                     |

| UART1_CLK                                     | Receive/transmit + edge detection                                                           |

| UART2_CLK                                     | Receive/transmit + edge detection                                                           |

| TIMER_CLK                                     | Demand signal for debug only. DMD_EN should not be set for the TIMER_CLK                    |

| SPIM_CLK                                      | Demand signal based on the read/write activity on APB                                       |

| SPIS_CLK                                      | Demand signal always at '1'                                                                 |

| DSU_CLK                                       | Demand signal signal always at '1' <sup>1</sup>                                             |

| MC_CLK                                        | Not in idle state, DMD_EN bit cleared by an irq pending                                     |

| CPU_CLK                                       | MC not in idle state, DMD_EN cleared by an irq pending                                      |

| GPIO_CLK                                      | Demand signal always at '1' <sup>1</sup>                                                    |

| Note 1: Demand signal always at '1' means the | t the DND EN hit has no effect on the clock. As long as CLK. EN is set the clock will be an |

Note 1: Demand signal always at '1' means that the DMD\_EN bit has no effect on the clock. As long as CLK\_EN is set, the clock will be on.

## 9 System Control Block

## 9.1 System Control Registers

| Address    | Name              | Туре       | Function                           |

|------------|-------------------|------------|------------------------------------|

| 0x800000F0 | SYS_CTRL_REG      | Read/write | Multi purpose system control       |

| 0x800000F4 | Reserved          |            |                                    |

| 0x800000F8 | CCTRL_BYTESEL_REG | Read/write | Sub-clocks and byte enable control |

| 0x800000FC | TEST_REG          | Read/write | Test and debug control             |

The system control block gathers registers with various purposes.

The SYS\_CTRL\_REG controls the clock division factor, sets the system into SLEEP mode, selects the input to the ADC converter, the mode of the GPIO port and enables the watchdog counter overflow to reset the system. It entails also some flags indicating a low backup battery voltage, the validity of the PPS signal and the presence of an antenna at the RF front-end side.

The CCTRL register controls each internally generated sub clock domain with two bits: the DMD\_EN (MSB) and CLK\_EN bit (LSB). The CLK\_EN has the highest priority and if set to '0' completely disable the sub clock domain. Once the sub clock domain has been activated (CLK\_EN='1') the activity is controlled by the peripheral clocked by the sub clock domain. With DMD\_EN = '0', the clock is always switched on, while if DMD\_EN = '1', the clock is controlled by a synchronous signal generated by the peripheral. By default all clocks are switched on and demand mechanism is disabled ('01').

#### Clock control

| DMD_EN | CLK_EN | Situation                                                         |

|--------|--------|-------------------------------------------------------------------|

| Х      | 0      | Clock is always switched off                                      |

| 0      | 1      | Clock is always switched on (default)                             |

| 1      | 1      | Clock is switched on by the peripheral served by the clock domain |

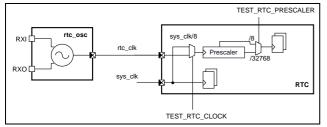

For test purposes, two bits in the TEST\_REG are available in order to speed up the RTC behavior. TEST\_RTC\_CLK permits to feed a SYS\_CLK divided by 4 into the 15 bits prescaler. The TEST\_RTC\_PRESCALER put the prescaler into a divide by 8 mode, in order to accelerate the execution of a functional RTC test. (See RTC chapter)

## 9.2 Register Details

#### SYS\_CTRL\_REG (Addr 0x800000F0)

| Field         | Bits  | Rst   | Description                                                                                                                                                               |  |  |

|---------------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RESERVED      | 31:15 | undef | Reserved bits                                                                                                                                                             |  |  |

| SYS_SPI_SLAVE | 14    | 0     | SPI master slave select. Selects the mode of the SPI external signals. Default is 0, Master.                                                                              |  |  |

| SYS_ANT_OK    | 13    | undef | Antenna OK. The value delivered by the RF front end is sampled into this register after three SYS_CLK cycles. '1' means that the antenna is present and working properly. |  |  |

| SYS_WD_RST_EN | 12    | 0     | Watchdog reset enable. If set, enables the execution of a system reset, when the watchdog counter overflows.                                                              |  |  |

| SYS_GPIO_MODE | 11:9  | 000   | Selects the mode of the GPIO port.                                                                                                                                        |  |  |

| SYS_ADC_SEL   | 8:6   | 000   | Select the input to the ADC converter. Default (000) is the on chip temperature sensor, while '001' to '111' select AIN[0] to AIN[6].                                     |  |  |

|               | 5     |       | Reserved                                                                                                                                                                  |  |  |

| SYS_LOW_BAT   | 4     | 0     | Low Backup Battery Flag. It is set when the VBAT signal is lower than 1.10V.                                                                                              |  |  |

| SYS_GO_SLEEP  | 3     | 0     | Go to Sleep. When set, this bit forces the system into sleep mode.                                                                                                        |  |  |

| SYS_CLK_DIV   | 2:0   | 111   | Clock division factor for the generation of the GPS_REF_CLK / NP1016_GPS_CLK.<br>Default is 111 = div by 8, 110 = div by 7 until 000 = div by 1.                          |  |  |

## CCTRL\_REG (Addr 0x800000F8)

NB: For each pair of bit of this register, the MSB is the DMD\_EN bit and the LSB is the CLK\_EN bit, as explained in the 'Clock control' table.

| Field                | Bits  | Rst   | Description                                                   |

|----------------------|-------|-------|---------------------------------------------------------------|

| RESERVED             | 31:24 | undef | Reserved bits                                                 |

| CCTRL_GPS_REF        | 23:22 | 01    | External GPS reference clock control                          |

| CCTRL_NP1016_APB_CLK | 21:20 | 01    | Control of the clock of the APB interface of the NP1016       |

| CCTRL_NP1016_GPS_CLK | 19:18 | 01    | Control of the GPS clock of the NP1016                        |

| CCTRL_UART2          | 17:16 | 01    | UART2 clock control                                           |

| CCTRL_UART1          | 15:14 | 01    | UART1 clock control                                           |

| CCTRL_TIMER          | 13:12 | 01    | TIMERs clock control. DMD_EN should never be set. Debug only. |

| CCTRL_SPIM           | 11:10 | 01    | SPI mater clock control                                       |

| CCTRL_SPIS           | 9:8   | 01    | SPI slave clock control                                       |

| BE_MODE              | 7     | 0     | Sets the external memory interface in byte enable mode        |

| CCTRL_DSU            | 6     | 1     | DSU clock control                                             |

| CCTRL_MC             | 5:4   | 01    | Memory controller clock control                               |

| CCTRL_CPU            | 3:2   | 01    | CPU clock control                                             |

| CCTRL_GPIO           | 1:0   | 01    | GPIO clock control                                            |

## TEST\_REG (Addr 0x800000FC)

| Field              | Bits | Rst   | Description                                                                                                                                             |

|--------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESERVED           | 31:9 | undef | Reserved bits                                                                                                                                           |

| TEST_SPI           | 8    | 0     | SPI test mode. When set, data from the slave is routed back to the master so that a back to back test of the master and slave devices can be performed. |

| TEST_DMD_SEL       | 7:2  | 0000  | Selects the internal clock demand signal to be muxed out to the DMD_OUT signal on the GPIO.                                                             |

| TEST_RTC_CLK       | 1    | 0     | If set, SYS_CLK divided by 8 is fed to the input of the RTC prescaler                                                                                   |

| TEST_RTC_PRESCALER | 0    | 0     | If set, the RTC prescaler is set into a divide by 8 mode.                                                                                               |

## **10 Interrupt Controller**

## 10.1 Interrupt Control Registers

| Address    | Name         | Туре       | Function                             |

|------------|--------------|------------|--------------------------------------|

| 0x80000090 | IRQMASK_REG  | Write      | Interrupt mask and priority register |

| 0x80000094 | IRQPEND_REG  | Read       | Interrupt pending register           |

| 0x80000098 | IRQFORCE_REG | Read/Write | Interrupt force register             |

| 0x8000009C | IRQCLEAR_REG | Write      | Interrupt clear register             |

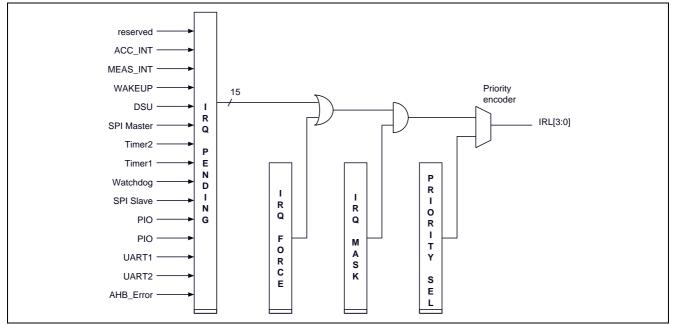

## Figure 5. Interrupt controller block diagram

## Interrupt assignments

| Source                          |

|---------------------------------|

| Reserved                        |

| ACC_INT from NP1016             |

| MEAS_INT from NP1016            |

| CPU_WAKE (RTC_WAKE or EXT_WAKE) |

| DSU                             |

| SPI Master                      |

| Timer 2                         |

| Timer 1                         |

| Watchdog                        |

| SPI Slave                       |

| GPIO interrupt – programmable   |

| GPIO interrupt – programmable   |

| UART1                           |

| UART2                           |

| AHB error                       |

|                                 |

The LEON interrupt controller is used to prioritise and propagate interrupt requests from internal or external devices to the integer unit. In total 15 interrupts are handled, divided on two priority levels.

## 10.2 Operation

When an interrupt is generated, the corresponding bit is set in the interrupt pending register. The pending bits are ANDed with the interrupt mask register and then forwarded to the priority selector. Each interrupt can be assigned to one of two priority levels as programmed in the interrupt level register. Level 1 has higher priority than level 0. The interrupts are prioritised within each level, with interrupt 15 having the highest priority and interrupt 1 the lowest. The highest interrupt from level 1 will be forwarded to the Integer Unit - if no unmasked pending interrupt exists on level 1, then the highest unmasked interrupt from level 0 will be forwarded. When the integer unit acknowledges the interrupt, the corresponding pending bit will automatically be cleared.

Interrupt can also be forced by setting a bit in the interrupt force register. In this case, the IU acknowledgement will clear the force bit rather than the pending bit.

## 10.3 Register Details

## IRQMASK\_REG (Addr 0x80000090)

| Field    | Bits  | Rst   | Description                                                                                                                                                                   |

|----------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ILEVEL   | 31:17 |       | Interrupt level - indicates whether an interrupt belongs to priority level 1 (ILEVEL[n]=1) or level 0 (ILEVEL[n]=0). Bit 31 corresponds to IRQ15, Bit 30 to IRQ14, and so on. |

| RESERVED | 16    | undef | Reserved bit                                                                                                                                                                  |

| IMASK    | 15:1  |       | Interrupt mask - indicates whether an interrupt is masked (IMASK[n]=0) or enabled (IMASK[n]=1).                                                                               |

| RESERVED | 0     | undef | Reserved bit                                                                                                                                                                  |

## IRQPEND\_REG (Addr 0x80000094)

| Field    | Bits  | Rst   | Description                                                                               |

|----------|-------|-------|-------------------------------------------------------------------------------------------|

| RESERVED | 31:16 | undef | Reserved bits                                                                             |

| IPEND    | 15:1  |       | Interrupt pending (IPEND[15:1]) - indicates whether an interrupt is pending (IPEND[n]=1). |

| RESERVED | 0     | undef | Reserved bits                                                                             |

## IRQFORCE\_REG (Addr 0x80000098)

| Field    | Bits  | Rst   | Description                                                                                    |

|----------|-------|-------|------------------------------------------------------------------------------------------------|

| RESERVED | 31:16 | undef | Reserved bits                                                                                  |

| IFORCE   | 15:1  |       | Interrupt force (IFORCE[15:1]) - indicates whether an interrupt is being forced (IFORCE[n]=1). |

| RESERVED | 0     | undef | Reserved bits                                                                                  |

## IRQCLEAR\_REG (Addr 0x8000009C)

| Field    | Bits  | Rst   | Description                                                                                                                                                                                                             |

|----------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESERVED | 31:16 | undef | Reserved bits                                                                                                                                                                                                           |

| ICLEAR   | 15:1  |       | Interrupt clear (ICLEAR[15:1]) - if written with a '1', ICLEAR[n] will clear IPEND[n] in the interrupt pending register. A consecutive read on ICLEAR[n] will return '0' and confirm that the pending has been cleared. |

| RESERVED | 0     | undef | Reserved bits                                                                                                                                                                                                           |

## 11 Timers and Watchdog

## 11.1 Timer Control Registers

| Address                 | Name               | Туре       | Function                       |

|-------------------------|--------------------|------------|--------------------------------|

| 0x80000040 / 0x80000050 | TIMER_CNTx_REG     | Read       | Timer value                    |

| 0x80000044 / 0x80000054 | TIMER_LOADx_REG    | ReadWrite  | Timer reload value             |

| 0x80000048 / 0x80000058 | TIMER_CTRLx_REG    | Read/Write | Timer general control register |

| 0x8000004C              | WDOG_CNT           | Read       | Watchdog value                 |

| 0x80000060              | PRESCALER_CNT_REG  | Read       | Prescaler counter              |

| 0x80000064              | PRESCALER_LOAD_REG | Read/write | Prescaler reload               |

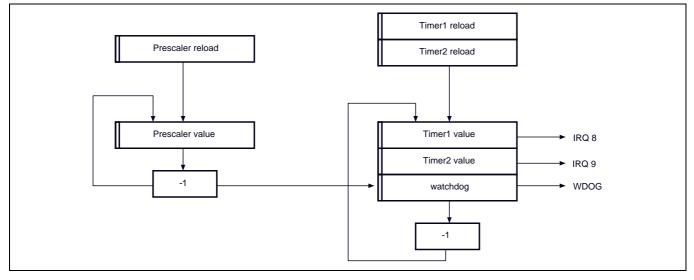

## Figure 6. Timer unit block diagram

The timer unit implements two 24-bit timers, one 24-bit watchdog and one 10-bit shared prescaler.

## 11.2 Operation

The prescaler is clocked by the system clock and decremented on each clock cycle. When the prescaler underflows, it is reloaded from the prescaler reload register and a timer tick is generated for the two timers and watchdog. The effective division rate is therefore equal to prescaler reload register value + 1.

The operation of the timers is controlled through the timer control register. A timer is enabled by setting the enable bit in the control register. The timer value is then decremented each time the prescaler generates a timer tick. When a timer underflows, it will automatically be reloaded with the value of the timer reload register if the reload bit is set, otherwise it will stop (at 0x000000) and reset the enable bit. An interrupt will be generated after each underflow. The timer can be reloaded with the value in the reload register at any time by writing a '1' to the load bit in the control register.

The watchdog operates similar to the timers, with the difference that it is always enabled. The watchdog output is connected to the reset control block.

For SW debugging the generation of the reset by the watchdog can be disabled by clearing the SYS\_WD\_RST\_EN bit in the SYS\_CTRL\_REG which allows to enable/disable the watchdog and trap the event leading to the watchdog overflow, avoiding a processor reset.

To minimise complexity, the two timers and watchdog share the same decrementer. This means that the minimum allowed prescaler division factor is 4 (reload register = 3).

## 11.3 Register Details

## TIMER\_CNTx\_REG (Addr 0x80000040 / 0x80000050)

| Field        | Bits  | Rst   | Description   |

|--------------|-------|-------|---------------|

| RESERVED     | 31:24 | undef | Reserved bits |

| TIMERx_VALUE | 23:0  | undef | Timer value   |

## TIMER\_LOADx\_REG (Addr 0x80000044 / 0x80000054)

| Field       | Bits  | Rst   | Description        |  |

|-------------|-------|-------|--------------------|--|

| RESERVED    | 31:24 | undef | Reserved bits      |  |

| TIMERx_LOAD | 23:0  | undef | Timer reload value |  |

## TIMER\_CTRLx\_REG (Addr 0x80000048 / 0x80000058)

| Field     | Bits | Rst   | Description                                                                                                         |  |

|-----------|------|-------|---------------------------------------------------------------------------------------------------------------------|--|

| RESERVED  | 31:3 | undef | Reserved bits                                                                                                       |  |

| TIMERx_LD | 2    |       | Load counter. When set, will load the timer reload register into the timer counter register. Always read as a '0'.  |  |

| TIMERx_RL | 1    |       | Reload counter. If set, then the counter will automatically be reloaded with the reload value after each underflow. |  |

| TIMERx_EN | 0    | undef | Enable. Enables the timer when set.                                                                                 |  |

## WDOG\_CNT\_REG (Addr 0x8000004C)

| Field      | Bits  | Rst   | Description            |  |

|------------|-------|-------|------------------------|--|

| RESERVED   | 31:24 | undef | Reserved bits          |  |

| WDOG_VALUE | 23:0  | undef | Watchdog counter value |  |

## PRESCALER\_CNT\_REG (Addr 0x80000060)

| Field     | Bits  | Rst   | Description             |  |

|-----------|-------|-------|-------------------------|--|

| RESERVED  | 31:10 | undef | Reserved bits           |  |

| PRESC_CNT | 9:0   | undef | Prescaler counter value |  |

## PRESCALER\_LOAD\_REG (Addr 0x80000064)

| Field      | Bits  | Rst   | Description            |  |

|------------|-------|-------|------------------------|--|

| RESERVED   | 31:10 | undef | Reserved bits          |  |

| PRESC_LOAD | 9:0   | undef | Prescaler reload value |  |

## 12 Real Time Clock (RTC)

## 12.1 RTC Control Registers

| Address    | Name           | Туре       | Function        |

|------------|----------------|------------|-----------------|

| 0x80008000 | RTC_TIME_REG   | Read/Write | Real Time Clock |

| 0x80008004 | RTC_WAKEUP_REG | Read/Write | Wake up value   |

Clocked by a dedicated 32.768 kHz oscillator the RTC is battery backed up, together with the NVRAM. The RTC has 1s resolution and doesn't overflow when the maximal value of  $2^{30}$  seconds is reached. The RTC is built with a 15 bits ripple carry prescaler that divides the 32.768 kHz clock followed by a synchronous 30 bit programmable counter.

For test purposes the rtc\_clock can be sped-up using the TEST\_RTC\_CLK and the TEST\_RTC\_PRESCALER bits of the TEST\_REG (see 'System Control block' section)

## Figure 7 RTC clock generation

The RTC has a precision of 1 second. The alarm function can be programmed by writing the wake-up time into a 30 bit register (RTC\_WAKEUP\_REG). If the RTC value is the same or bigger than the alarm value, then the RTC\_WKUP event is generated, which is usually used to recover from a sleep mode. The RTC\_WKUP is also connected to the CPU interrupt controller.

The CPU can set the RTC time by writing to the RTC\_TIME\_REG register and gets the RTC value by reading from the same address. The RTC\_TIME\_REG is automatically updated with the latest RTC counter value (RTC\_VALUE) at each tick of the 32.786kHz RTC clock. The max uncertainty on the time switching from one second to the following one, has been calculated in 45msec.

The RTC\_TIME\_REG register is double buffered so that it can be written at system clock speed. However the value is transferred from the system accessible RTC\_TIME\_REG register to the RTC internal register synchronously to the 32 KHz RTC Clock.

As physically writing to the RTC counter may take up to 1.5 RTC clock cycles, the APB\_RTC logic is designed to handle this latency automatically. The RTC\_TIME\_REG register can be updated without taking care of the timing of the RTC counter. The RTC\_WRFLAG acts as a write completed flag. If RTC\_WRFLAG is set by the software, it will be automatically cleared when the update of the RTC counter with the new RTC\_VALUE has been completed. Then, the RTC\_WRFLAG can be polled in the interval to check the progress of the write.

A wake up value can be set with the RTC\_WAKEUP\_REG register. A value of the RTC counter equal or higher than the RTC\_WAKEUP\_TIME value will set the RTC\_WKUP bit in the RTC\_TIME\_REG register and send a wake-up signal to the powerup unit. RTC\_WKUP is also connected to IRQ 12 of the interrupt controller.

Accesses to the RTC\_WAKEUP register occur at system clock speed, this register is not shadowed and comparisons to the RTC\_TIME\_REG are performed in the RTC clock domain, hence it is possible for updates of the RTC\_WAKEUP\_REG register to cause a spurious RTC\_WKUP event. Therefore the RTC wakeup interrupt must be masked when updating the RTC\_WAKEUP\_REG register.

## 12.2 NVRAM

The 2k x 32 bit battery backed-up SRAM is mapped at addresses 0x80002000 - 0x80003FFF in the APB space and is only accessible through 32 bits data words.

Data integrity as well as safe power supply switching to VBAT on failing DVDD or LVDD power supply is guaranteed by the Power Supervisor block.

The internal POWER\_OK signal generated by the Power Supervisor block is used to disable any access from the CPU during the transition phase from valid power supply to invalid power supply.

However if the switching to VBAT occurs during a write operation to the NVRAM, invalid or partially written data blocks could be stored in the NVRAM. Hence, the SW routines for the NVRAM access must implement a data integrity check mechanism that detects corrupted data blocks.

## 12.3 Power Fence

A power fence logic is introduced between the APB interface and the part consisting of the NVRAM macro and the RTC circuits. The power fence guarantees that with any voltage between 0V and LVDD on one side and any voltage between 0V and LVDD max or 0 and VBAT max on the other, no gates are damaged. When power is lost or an asynchronous reset occurs, the power fence forces to a pre-determined level the internal NVRAM control signals while all outputs from the memory and RTC are gated to 0.

## 12.4 Register Details

## RTC\_TIME\_REG (Addr 0x80008000)

| Field      | Bits | Rst | Description                                                                                                                                                                         |

|------------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTC_WRFLAG | 31   | 0   | "Write has occured" flag. This flag is automatically cleared when the RTC_VALUE has been written to the RTC counter. It can be polled to check if the write operation is completed. |

| RTC_WKUP   | 30   | 0   | Wake-up match flag. Indicates that the RTC wake-up value has been reached (i.e RTC_VALUE $\ge$ RTC_WAKEUP_TIME). Must be cleared manually.                                          |

| RTC_VALUE  | 29:0 | NA  | RTC counter value. The value written here will be transferred to the RTC counter at the next edge of the RTC clock. These bits also reflect the current value of the RTC counter.   |

## RTC\_WAKEUP\_REG (Addr 0x80008004)

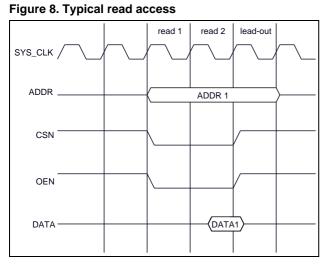

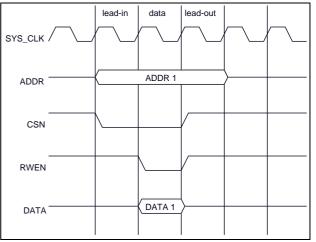

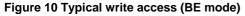

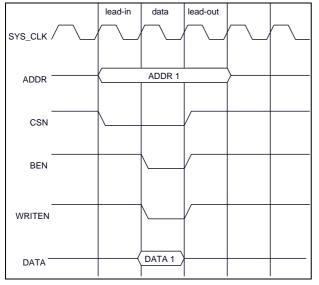

| Field           | Bits  | Rst   | Description                                                                                                                                                   |  |  |